系統工程師正受到降低成本和提高電路板可靠性的壓力。一個經常被忽視的應對措施是減少為 FPGA、 微處理器和數位訊號處理器進行電源監控而使用的元件數量。

新穎的高整合度可編程電源電路將重定產生、看門狗計時器(WDT)和電壓監控器 IC 整合在單個元件之中。這種更高水淮的一體化方案有助于降低系統成本,解決了

PCB設計人員所關心的可靠性問題。本文探討了將可編程邏輯, ADC 和 DAC 合并的創新解決方案,它使電源管理功能具有更高的精確性,同時還降低了成本。

電源管理的挑戰

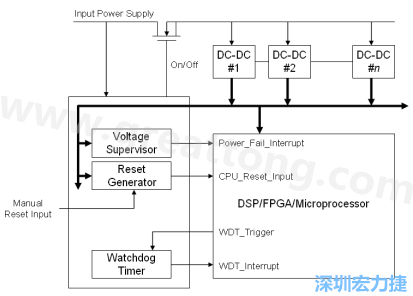

一個典型的 CPU 電源電路如圖一所示。對于典型的 DSP、 FPGA 或微處理器而言,各種電源電壓要求為:元件的核心電壓為 1.2V、輔助電壓和 PLL 電壓為 3.3V、 I/O 驅動電壓為 1.5V 和 1.8V。常見的供給設計的電壓是源于單一的 5V 輸入電源,透過一系列 DC-DC轉換器提供各種電源電壓。為了提供如同單電源印刷電路板一樣的可靠性,必須對電路板上的所有電源進行監測,并能產生正確的 CPU 重定信號或電源故障中斷信號。

圖一 典型的電源管理電路

圖一所示的電壓監控區塊是一顆 IC,電源發生故障時,或手動切斷電路板的電源,它會發訊號給 CPU。如果任何一個 DC-DC 轉換器發生故障,會引起電壓升高或降低,超出正常工作電壓的范圍,這會導致 CPU 不能正常執行程序。

對 CPU 而言,一個潛在的最糟糕情況是非揮發性記憶體被改寫,使系統無法啟動。如果電源發生故障時,能夠中斷 CPU,那么就能安全地中止當前的任務,為可靠的重新啟動保存重要的資訊。

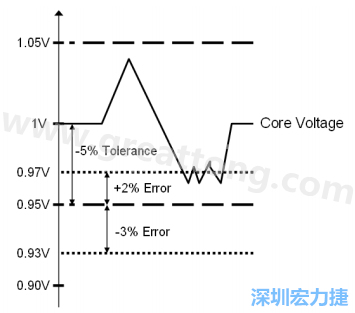

許多廉價的電壓監控器 IC 通常有一個被忽視的負作用,對于電壓變化,監控器的閾值將影響整個系統的容差。圖二說明了這種情況,核心電壓的規格為 1V +/-5% 。如果 CPU 核心電壓低于 0.95V,就要求監控器必須發出一個中斷訊號。

然而,考慮監控器的閾值精度,電壓變化的整個容差降低了。在這個例子中,該監控器的閾值為 0.95V+2%/-3% (0.97V~0.93V)。使用這種監控 IC 時,該閾值應設置成 0.97V ,這就限制了 DC-DC 轉換器的容差。

圖 2 核心電壓規范與監控器閾值的比較

圖一中的重定發生區塊是另一種較常見的離散 IC,當所有電壓穩定后,它向 CPU 發出釋放重定輸入訊號。在所有電源穩定之后,CPU 繼續保持重定模式一段時間是常見的情況。例如,Power Good 信號有效后,Intel Atom 處理器期待“脈沖延伸”兩個毫秒的復位脈沖。只有到那個時刻,CPU 才開始執行程序。

圖一的最后一顆離散 IC 是看門狗計時器。如果主程序沒有對監視器進行定期服務,這個計時元件觸發系統重定。其目的是將系統從暫停狀態恢復為正常運行。

提升電源管理的靈活性并降低成本

有各種各樣的電源,復位和看門狗計時器應用的需求,因此這些情況已導致元件供應商提供大量的離散數位和混合訊號元件,旨在幫助PCB設計人員應對電源管理的挑戰。但是,采用離散式電壓監控器、重定和計時器電路會增加印刷電路板布局的復雜性,還會提高成本。

由于板級寄生作用和電源的開關,電壓波動是正常的電源特性,設計師采用的削減成本的措施之一是使用不太精確、成本更低的電壓監控元件。然而,變化超過 1%的廉價監控器閾值會降低系統的電源紋波容差,并導致重定條件比實際需要多。

在一些設計中,另一個降低成本的措施是不監測所有的電壓幅度,期望在正常工作期間,DC-DC 轉換器沒有故障。這是另一個例子,雖然降低了成本,可靠性卻受到了損害。電路板的變化往往迫使PCB設計人員重新設計電源管理電路,每次設計都要使用各種零組件。

使用功能固定的離散 IC 的重新設計,常常意味著要備有更多合格的元件,形成了很大的庫存量。

許多電源管理電路設計存在著固有的缺點,因而設計者萌生了將復雜可編程元件與高精度類比電路整合在同一元件上的想法。可編程元件為狀態機或布林邏輯描述的各種邏輯時序提供了靈活性。有非常精確的可編程中斷點的改進型閾值監控器,使同一晶片可用于更廣泛的電源監控應用。總之,可編程的電源管理積體電路可幫助PCB設計人員使具有普遍性的電源管理解決方案標淮化。

可編程電源管理 IC 實例

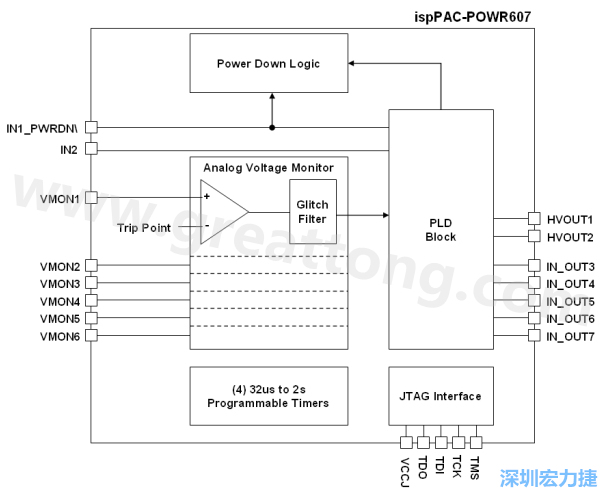

萊迪思半導體的 Power Manager II 是高整合度的產品,而且提升了許多板級監控積體電路的精確性。這些電源管理元件將精密故障監測電路、CPLD 和 ADC/DAC 電路集整合于同一元件中。例如, Power Manager II 中的一個產品可監控多達 6 個電源,并提供 7 個數位輸出。使用具有 4 個可編程計時器的可編程邏輯元件區塊,該元件可以產生 CPU 重定信號,包括脈沖延伸和電源故障中斷信號。

7 個輸出中的兩個可配置成高電壓 MOSFET 驅動器,另外 5 個輸出可配置成輸入。還有兩個通用數位輸入端,可用于其他控制功能(參考圖三 ) 。

圖 3 POWR607 結構圖

這種整合電源 IC 取代了如前所述的三個電壓監控器、重定發生器和看門狗計時器電源管理 IC,而且成本較低。在某些情況下,甚至取代兩個離散 IC 可能會得到一個更經濟的設計。電源管理 IC 的整合性能不但有助于節省時間和經費,而且還可用于多種設計。

Power Manager II POWR607 元件的 6 個電壓監控器( VMON )都是可以獨立可編程的。中斷點比較器提供 192 可編程點,整個范圍為 0.667V 到 5.811V 。電源關閉之后,每個都提供一個 75mV 零檢測選擇,以確定電源輸出是否已經衰退到無效的情況。當電源關閉時,如果被監測的電壓大于中斷點設置,每個比較器輸出一個邏輯高電平至可編程元件。

比較器提供設定點的滯回約 1%,以減少由電路板引入的輸入雜訊造成的誤觸發,以及由于開關電源而引起的正常電源紋波。過電壓和欠電壓斷路點是可編程的,反映了被管理的DSP/FPGA/微控制器的容差。

每顆電壓監控器提供了一個數位濾波器,可以延時比較器的輸出,以避免假的觸發條件。

針對 CPU 的看門狗計時器功能提供了一個內置的振盪器和可編程計時器電路,設定時序間隔范圍為 32 微秒到 2 秒 。

已經證實 Power Manager II 元件對從事數位系統設計的工程師以及類比電源設計者頗具吸引力,它提供了一個簡單的軟件可編程界面。一個示意框圖可以讓設計者用對話方塊配置類比區塊,一個方程構造器就能夠容易地構建復位時序。

該元件提供了在系統編程(ISP)的 JTAG 界面,并可支援標淮的 JEDEC 檔案格式。 當元件已安裝在電路板上時,可透過 ISP 界面對電路的功能進行修改或升級。透過 JTAG 鏈,它比傳統的離散 IC 具備更好的可見度。

可重復編程電源管理器的概念有助于加速修改已有的電路板,還能減輕修改新設計的負擔。透過對大多數電源管理應用中使用的離散 IC 的整合,可編程電源管理晶片不但提供了更好的靈活性,而且降低了零件材料成本。

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產 | PCBA代工代料