下面利用SI9000計算是否達到阻抗控制的要求:

首先計算DDR數據線的單端阻抗控制:

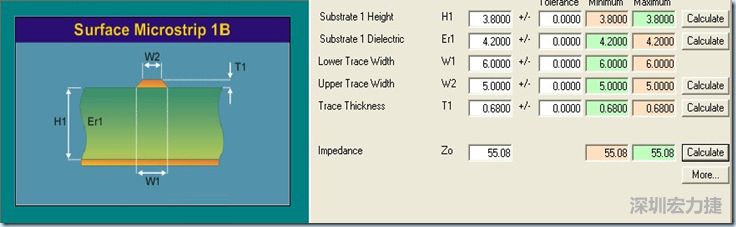

TOP層:銅厚為0.5OZ,走線寬度為5MIL,距參考平面的距離為3.8MIL,介電常數為4.2。選擇模型,代入參數,選擇lossless calculation,如圖所示:

計算得到單端阻抗為Zo=55.08ohm,與要求相差5歐姆。根據板廠的反饋,他們將走線寬度改為6MIL以達到阻抗控制,經過驗證,在寬度W2=6MIL,W1=7MIL的情況下,計算得到的單端阻抗為Zo=50.56歐姆,符合設計要求。

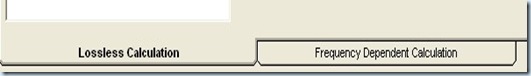

L2層:在L2層的走線模型如下圖所示:

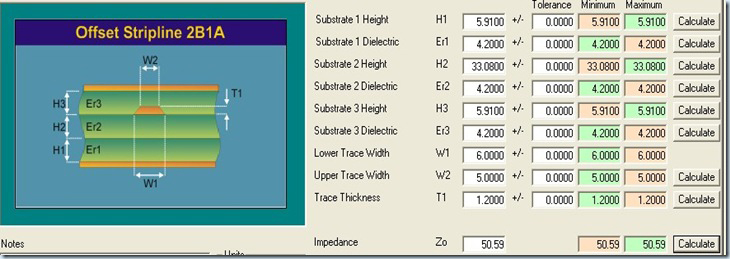

代入參數進行計算得到如下圖所示:

計算得到單端阻抗為Zo=50.59歐姆,符合設計要求。

同理可以得到L3層的單端阻抗,在此不再贅述。

下面計算差分阻抗控制:

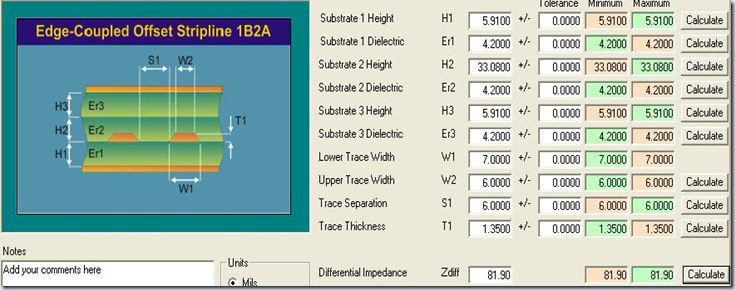

由PCB設計可知,底板PCB中時鐘走線在L3層,USB數據線在L2層,走線寬度均為6MIL,間距為6MIL。

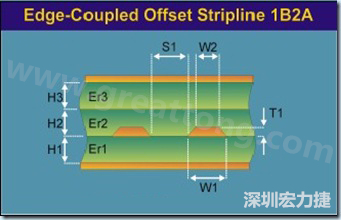

時鐘信號選擇的模型如下所示:

按照提供給板廠的數據計算得到的結果如下圖所示:

根據板廠的反饋,差分阻抗只能做到85歐姆,與計算結果接近(他們可以微調板層厚度,但不能調線)。但是改變線間距為12MIL時,計算得到的差分阻抗為92.97歐姆,再將線寬調為5MIL時,差分阻抗為98.99歐姆,基本符合設計要求。

經驗小結

1、當差分走線在中間信號層走線時,差分阻抗的控制比較困難,因為精度不夠,就是說改變介質層厚度對差分阻抗的影響不大,只有改變走線的間距才對差分阻抗影響較大。但是當走線在頂層或底層時,差分阻抗就比較好控制,很容易達到設計要求,通過實際計算發現,重要的信號線最好走表層,容易進行阻抗控制,尤其是時鐘信號差分對。

2、在PCB設計之前,首先必須通過阻抗計算,把PCB的疊層參數確定,如各層的銅厚,介質層的厚度等等,還有差分走線的寬度和間距都需要事先計算得出,這些就是PCB的前端仿真,保證重要的信號線的阻抗控制滿足設計要求。

3、關于介電常數Er的問題:

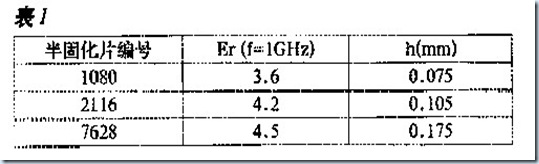

以我們使用最多的FR-4介質的材料板為例:實際多層板是芯板和壓合樹脂層堆疊而成,其芯板本身也是由半固化片組合而成。常用的三種半固化片技術指標如下表1 所示。

半固化片組合的介電常數不是簡單的算術平均,甚至在構成微帶線和帶狀線時的Er值也有所不同。另一方面,FR-4的Er也隨信號頻率的變化有一定改變,不過在1GHz 以下一般認為FR-4 材料的Er 值約4.2。通常計算時采用4.2。

4、在實際的阻抗控制中,一般采用介質為FR-4,其Er約4.2,線條厚度t對阻抗影響較小,實際主要可以調整的是H和W,W(設計線寬)一般情況下是 由設計人員決定的,但在設計時應充分考慮線寬對阻抗的配合性和實際加工精度。當然,采用較小的W 值后線條厚度t 的影響就不容忽視了。H(介質層厚度)對阻抗控制的影響最大,實際H 有兩類情況:一種是芯板,材料供應商所提供的板材中H的厚度也是由以上三種半固化片組合而成,但其在組合的過程中必然會考慮三種材料的特性,而絕非無條件 的任意組合,因此板材的厚度就有了一定的規定,形成了一個相應的清單,同時H 也有了一定的限制。如0.17mm 1/1的芯板為 2116 ×1,0.4mm 1/1的芯板為1080×2+7628×1等。另一種是多層板中壓合部分的厚度:其方法基本上與前相同但需注意銅層的損失。如內電層間用半固化片進行填 充,因在制作內層的過程中銅箔被蝕刻掉的部分很少,則半固化片中樹脂對該區的填充亦很少,則半固化片的厚度損失可忽略。反之,如信號層之間用半固化片進行 填充,由于銅箔被蝕刻掉的部分較多,則半固化片的厚度損失會很大且難以估計。因此,有人建議在內層的信號層要求鋪銅以減少厚度損失。

5、特征阻抗與傳輸線的寬度是成反比的,寬度越寬,阻抗越低,反之則阻抗更高。

6、在有些板的設計要求中對板層厚度有限制時,此時要達到比較好的阻抗控制,采用好的疊層設計非常關鍵。從實際的計算中可以得出以下結論:

a. 每個信號層都要有參考平面相鄰, 能保證其阻抗和信號質量;

b. 每個電源層都要有完整的地平面相鄰, 使得電源的性能得以較好的保證;

7、關于差分走線的線寬和間距對阻抗控制的討論:

通過軟件計算發現,改變差分對的間距對阻抗控制的影響較大,但是這里涉及到另一個問題,就是差分對的耦合問題。

差分對耦合的主要目的是增強對外界的抗干擾能力和抑止EMI。耦合分為緊耦合方式( 即差分對線間距小于或等于線寬) 和松耦合方式。

如果能保證周圍所有的走線離差分對較遠(比如遠遠大于3 倍的線寬),那么差分走線可以不用保證緊密的耦合,最關鍵的是保證走線長度相等即可。(可以參見Johnson 的信號完整性網站上的關于差分走線的闡述,他就要求他的layout 工程師將差分線離得較遠,這樣可以方面繞線)。只是目前大多數多層高速的PCB板走線空間很緊密,根本無法將差分走線和其它走線隔離開來,所以這時候保持緊密的耦合以增加抗干擾能力是應該的。

緊耦合不是差分走線的必要條件,但是在空間不夠時走線采用緊耦合方式能夠增強差分走線的抗干擾能力。因此,對于差分對的阻抗控制問題,怎么調節各個參數需要綜合考慮上述因素,擇優選擇。一般情況下不輕易調整差分對的間距和線寬。

延伸:差分對走線的PCB要求

1、確定走線模式、參數及阻抗計算

差分對走線分外層微帶線差分模式和內層帶狀線差分模式兩種,通過合理設置參數,阻抗可利用相關阻抗計算軟件(如POLAR-SI9000)計算也可利用阻抗計算公式計算。

2、走平行等距線

確定走線線寬及間距,在走線時要嚴格按照計算出的線寬和間距,兩線間距要一直保持不變,也就是要保持平行。平行的方式有兩種: 一種為兩條線走在同一線層(side-by-side),另一種為兩條線走在上下相兩層(over-under)。一般盡量避免使用后者即層間差分信號, 因為在PCB板的實際加工過程中,由于層疊之間的層壓對準精度大大低于同層蝕刻精度,以及層壓過程中的介質流失,不能保證差分線的間距等于層間介質厚度, 會造成層間差分對的差分阻抗變化。困此建議盡量使用同層內的差分。

3、緊耦合原則

在計算線寬和間距時最好遵守緊耦合的原則,也就是差分對線間距小于或等于線寬。當兩條差分信號線距離很近時,電流傳輸方向相反,其磁場相互抵消,電場相互耦合,電磁輻射也要小得多。

4、走短線、直線

為確保信號的質量,差分對走線應該盡可能地短而直,減少布線中的過孔數,避免差分對布線太長,出現太多的拐彎,拐彎處盡量用45°或弧線,避免90°拐彎。

5、不同差分線對間處理

差分對對走線方式的選擇沒有限制,微帶線和帶狀線均可,但是必須注意要有良好的參考平面。對不同差分線之間的間距要求間隔不能太小,至少應大于3~5倍差分線間距。必要時在不同差分線對之間加地孔隔離以防止相互問的串擾。

6、遠離其它信號

對差分對信號和其它信號比如TTL信號,最好使用不同的走線層,如果因為設計限制必須使用同一層走線,差分對和TTL的距離應該足夠遠,至少應該大于3~5倍差分線間距。

7、差分信號不可以跨平面分割

盡管兩根差分信號互為回流路徑,跨分割不會割斷信號的回流,但是跨分割部分的傳輸線會因為缺少參考平面而導致阻抗的不連續(如圖箭頭處所示,其中GND1、GND2為LVDS相鄰的地平面)。

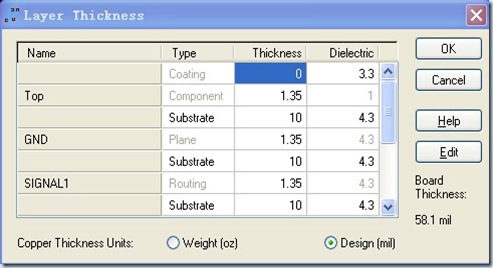

8、PADS LAYOUT中層定義選項卡各個參數的解釋說明:

coating表示涂覆層,如果沒有涂覆層,就在thickness 中填0,dielectric(介電常數)填1(空氣)。

substrate表示基板層,即電介質層,一般采用FR-4,厚度是通過阻抗計算軟件計算得到,介電常數為4.2(頻率小于1GHz時)。

點擊Weight(oz)項,可以設定鋪銅的銅厚,銅厚決定了走線的厚度。

9、絕緣層的Prepreg/Core的概念:

PP(prepreg)是種介質材料,由玻璃纖維和環氧樹脂組成,core其實也是PP類型介質,只不過他的兩面都覆有銅箔,而PP沒有,制作多層板時,通常將CORE和PP配合使用,CORE與CORE之間用PP粘合。

10、PCB疊層設計中的注意事項:

(1)、翹曲問題

PCB的疊層設計要保持對稱,即各層的介質層厚、鋪銅厚度上下對稱,拿六層板來說,就是TOP-GND與BOTTOM-POWER的介質厚度和銅厚一致,GND-L2與L3-POWER的介質厚度和銅厚一致。這樣在層壓的時候不會出現翹曲。

(2)、信號層應該和鄰近的參考平面緊密耦合(即信號層和鄰近敷銅層之間的介質厚度要很小);電源敷銅和地敷銅應該緊密耦合。

(3)、在很高速的情況下,可以加入多余的地層來隔離信號層,但建議不要多家電源層來隔離,這樣可能造成不必要的噪聲干擾。

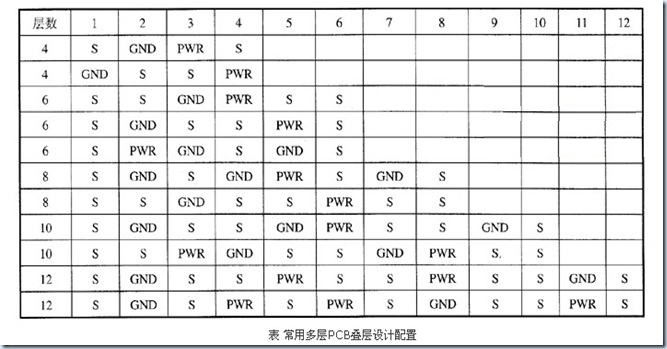

(4)、典型的疊層設計層分布如下表所示:

(5)、層的排布一般原則:

元件面下面(第二層)為地平面,提供器件屏蔽層以及為頂層布線提供參考平面;

所有信號層盡可能與地平面相鄰;

盡量避免兩信號層直接相鄰;

主電源盡可能與其對應地相鄰;

兼顧層壓結構對稱。

對于母板的層排布,現有母板很難控制平行長距離布線,對于板級工作頻率在50MHZ 以上的

(50MHZ 以下的情況可參照,適當放寬),建議排布原則:

元件面、焊接面為完整的地平面(屏蔽);

無相鄰平行布線層;

所有信號層盡可能與地平面相鄰;

關鍵信號與地層相鄰,不跨分割區。

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產 | PCBA代工代料